# CIRCUIT SWITCHING NETWORK ON CHIP FOR ERROR DETECTION BASED ON DISTANCE VECTOR ROUTING ALGORITHM

M.AYISHA SITHIKA STUDENT, ME VLSI DESIGN J.P COLLEGE OF ENGINEERING Mr.D.YOVAN SNANAGAN PONSELVAN Asst PROFESSOR J.P COLLEGE OF ENGINEERING

## **ABSTRACT**

Circuit-switched networks give secure transmission latency and output, and thus appropriate for several network-on-chip (NoC) requiring quality-of-service. Α circuit-switched on-chip network wants a computer architectures hardware to rearrange communication ways and assign a correct information measure for every path. Such a computer hardware offers a good answer for a essential step within the NOC style during this paper, we have a tendency to propose Associate in Nursing economical computer hardware for pre-scheduled circuit-switched on chip networks. supported simulations, we have a tendency to show that low delivery latency for circuit switched on-chip networks will be achieved with our computer hardware the projected NOC relies on new error detection mechanisms appropriate for dynamic NoCs, wherever the quantity and position of processor parts or faulty blocks vary throughout runtime. Indeed, we have a tendency to propose on-line detection of knowledge packet adjustive routing rule errors. Each best owed mechanism are ready to distinguish permanent and transient errors accurately the position of the faulty blocks (data bus. input port. output the NOC routers, whereas conserving the output, the network load, and therefore the information packet latency. we offer localization capability analysis of the bestowed mechanisms, NOC performance evaluations, and field-programmable gate array.

## INTRODUCTION

System on a chip (SoC) is that the style methodology presently utilized by VLSI designers, based on intensive information science core recycle. Cores don't compose SoCs alone, they have to embrace associate degree interconnection design and interfaces to peripheral devices [1] Usually, the interconnection design is predicated on dedicated wires or shared buses .Dedicated wires ar effective just for systems with alittle variety of cores, since the number of wires within the system will increase dramatically because the variety of cores grows. Therefore, dedicated wires have poor reusability and suppleness. A shared bus could be a set of wires common to multiple cores. This approach is a lot of scalable and reusable, compared to dedicated wires. However, busses permit only 1 communication dealings at a time. Thus, all cores share identical communication information measure within the system and measurability is restricted to a few dozens information science cores [2]. exploitation separate busses interconnected by bridges or hierarchal bus architectures could cut back a number of these constraints, since totally different busses could account for different information measure desires, protocols and additionally increase communication correspondence. Nonetheless, measurability remains a retardant for hierarchal bus architectures. A network on chip (NoC) seems as a most likely higher resolution to implement future on-chip interconnection architectures [2]-[7]. within the most ordinarily found organization, a NoC is a set of interconnected switches, with information science cores connected to those switches. NoCs gift higher performance, bandwidth, and measurability than shared busses [3].

Generally, these rules correspond to a changed routing algorithm that enables faulty or unavailable regions to be bypassed. Within the case of adjustive routing algorithms supported the flip model zones are outlined such as faulty nodes or unavailable regions already detected within the NOC. The neighboring routers of those zones should not send information packets these identified faultyroutersor unavailable regions. Many solu tions are projected to attain this constraint. One answer is to incorporate a routing table containing the output port to use for every destination within the network [13]. These tables are updated by Associate Nursing initialisation rule. The downside of most this answer is that the demand to invoke the rule at a non such time so as to update the routing tables of the NOC routers. Another answer typically applied is the use of chains and rings fashioned round the adjacent faulty nodes regions, so rectangular elements within the NOC covering all the faulty nodes or unavailable regions. These chains or rings of switches modify the routing tables, that so take issue

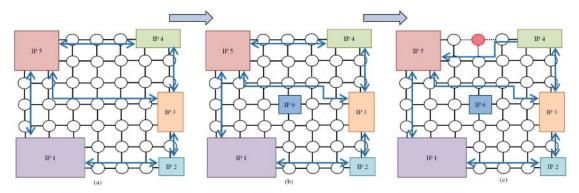

Fig. 1. Illustration of a dynamic reliable NoC. (a) Normal operation. (b) Dynamic implementation of an IP. (c) Online detection of a faulty router.

from the quality tables realizing the routing rule. These specific switches integrate in their tables extra routing rules that enable the faulty zones and regions dedicated to dynamic IP/PE instantiations to be by passed, whereas avoiding starvation, deadlock, and livelock things [3], [12], [14]. Another reliable routing rule answer is that the use of the deBruijn graph [15]. This rule is deadlock-free and handles the bypassing of faulty links between 2 switches by presumptuous that nodes are tuned in to the link that's connected to them by the employment of a detection mechanism. However. these solutions don't offer the mechanism to observe a faulty link or router. With respect to the increasing quality and therefore the reliableness evolution of SoCs, MPSoCs have become a lot of sensitive to phenomena that generate permanent, transient, or intermittent faults [16]. These faults could generate information packet errors, or could have an effect on router behavior resulting in information packet losses or permanent routing errors [17]. Indeed, a fault in a very routing logic can usually result in packet routing errors and would possibly even crash the router. To observe these errors, specific error detection blocks ar needed within the network to find the faulty sources. Indeed, the precise location of permanent faulty elements of the NOC should be determined, in order for them to be bypassed effectively by the adjustive routing rule.

To protect information packets against errors, error correcting codes (ECCs) square measure enforced within the secret agent elements. Among the accepted solutions, square measure typically applied for the MPSoC communications based mostly secret agent. First, the end-to-end resolution needs associate degree error correction code to be enforced in every input port of the IPs or PEs within the secret agent [18]. The most downside of this resolution is its incapacity to find the faulty elements (PE, IP, router, data bus, etc.) within the secret

agent. Consequently, it's inadequate for dynamic NoCs, wherever the faulty and unobtainable zones should be bypassed. Second, the switch-to switch detection relies on the implementation of associate degree error correction code in every input port of the secret agent switches. for example, during a router of 4 communication directions (North, South, East, and West), four error correction code blocks square measure enforced. Therefore, once a router receives an information packet from a neighbor, the error correction code block analyzes its content to visualize the correctness of the info. This method detects and corrects information errors in step with the effectiveness of the error correction code being employed. Third, another projected resolution is that the code disjoint [18]. During this approach, routers embody one error correction code in every input and output information port. This resolution localizes the error sources, which might be either within the switches or on the info links between routers. However, if a blunder supply is localized within a router, this resolution mechanism disables the totality of the switch. These on-line detection mechanisms cannot disconnect simply the faulty components of the secret agent, associate degreed thence don't provide an correct localization of the supply of errors. The result's that the network turnout decreases whereas the network load and information packet latency increase. Moreover, they're ineffectual to tell apart between permanent and transient errors. For of these techniques, every error correction code enforced within the routers of the network adds price in terms of logic space, latency in information packet transmission, and power consumption. Associate degree analysis of the supply and destination addresses, as conferred in [19], is among the techniques typically projected to be ready to find faulty routing choices. once a router receives an information packet, it compares its own address to the destination and supply addresses. Then, the router checks its own position within the settled path of the NoC for the

thought-about information packet. The router performing arts this checking is in a position to come to a decision whether or not the switch from that the packet was received created a routing error or not according to the proper path. However, this system encompasses a major drawback; it's unable to handle the bypass of faulty nodes and unobtainable regions. Consequently, this resolution can't be applied in adaptive or fault-tolerant routing algorithms. Indeed, as laid out in a flip model formula [12], the structure of the reconfigurable secret agent could contain bypass areas during which the switches take routing choices otherwise from the space vector routing formula. For handling message routing errors in dynamic networks, a brand new faulty switch detection mechanism is adaptive needed for or fault-tolerant algorithms. During this paper, we have a tendency to gift a brand new reliable dynamic secret agent. The projected secret agent could be a mesh structure of routers ready to find routing errors for adaptive routing supported the distance vector routing formula[3], [12], [14], [20]. Our approach includes information packet error detection and correction. The thought-about routing formula relies on the adaptive flip model routing theme and therefore distance vector routing algorithm is used. This adaptive formula is live lock-and deadlock-free and permits information packets to pass around faulty regions. Section II describes the design of the projected reliable switch. Section III details the projected routing error detection appropriate for adaptive routing algorithms. Section IV presents a selected self-loopback mechanism permitting the rejection of information packet loss, the maintaining of the performance of the secret agent, and therefore the effectively localizing of permanent sources of knowledge packet errors. Section V presents FPGA synthesis and secret agent performance evaluations, whereas Section VI validates the projected techniques by giving NoCs lustiness and localization capability of the error detection mechanisms.

## BASIS OF THE RKT-SWITCH

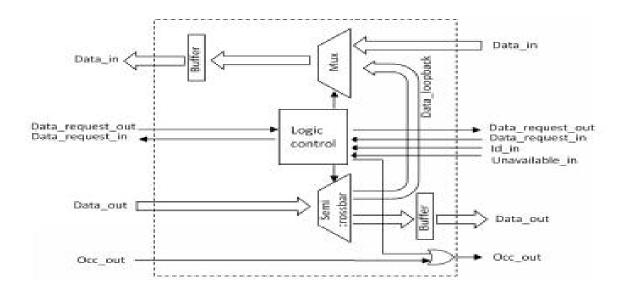

The design of the RKT switch is portrayed in Fig. 2. The RKT-switch is characterised by its design having four directions (North, South, East, West) appropriate for a 2-D mesh secret agent. The PEs and IPs will be connected on to any aspect of a router. Therefore, there's no specific association port for a letter of the alphabet or information science. The projected detection mechanisms also can be applied to NoCs victimisation 5 port routers with an area port dedicated to associate degree information science. However, the most important downside of those architectures is once the native port encompasses a permanent error and therefore the information science connected thereto is lost or must be dynamically affected within the chip thanks to the dynamic partial reconfiguration. On the contrary, for the four-port RKT

secret agent, associate degree information science will replace many routers by having many input ports and thence be powerfully connected within the network [5]. Moreover, by victimisation dynamic partial reconfiguration and IPs powerfully connected within the secret agent, nobody fault location is additional ruinous than another. Indeed, associate degree information science could have access to the network by being connected to many routers, or will be dynamically affected on the chip if this solely access purpose becomes faulty. every port direction consists of 2 unfacial information buses (input and output ports). every input port is associated to a first-input, first-output (FIFO) (buffers) and a routing logic block. The RKT-switch operation relies on the store-andforward switch technique. This system is appropriate for dynamically reconfigurable NoCs. Indeed, in our NoC, PEs and IPs will be enforced in situ of 1 or many routers [7]. At any instant with the shop and forward technique, every information packet is keep solely during a single router. Hence, once a router must be reconfigured, the router is barely needed to empty its buffers. On the contrary, with the hollow switch technique [14], one information packet will be cover many routers. Consequently, the time needed to clear all the routers containing partial packet information (flits) and to reconstruct these packets before performing arts a reconfiguration is additional important. The RKT secret agent uses non bouncing routers [21], in order that if a router is enclosed by 3 unobtainable nodes, the packet can't be routed. The info flow management employed in our design is that the Ack/Nack resolution, which might handle fault-tolerant transmissions [22], though this will increase the energy consumption [23]. This resolution depends on the retransmission of packets being received as faulty by a neighboring node having the ability to perform a packet retransmission when it's been sent to a node needs that a replica of the packet be domestically saved till associate degree Ack / Nack is received. If a neighboring router receives a flit containing a blunder that can't be corrected by the error correction code, a Nack is shipped back and therefore the whole packet is retransmitted. Otherwise, associate degree Ack is generated at full packet reception additional exactly, associate degree Ack is generated only if all the flits of the info packet are received and checked by the router, that reduces latency. The playacting error correction code is taken into account for our RKT-switch, so as to produce a convenient trade-off between space overhead and error correction capability. This alternative permits the correction of single event upset (SEU) errors (one bit flip during a flit) and therefore the detection of multiple event upset (MEU) errors (two bit flips during a flit). Moreover, the playacting code is additional appropriate for NoCs supported Ack/Nack flow management than the check bit check. Indeed, on one bit-flip

error incidence, error correction is feasible with the playacting error correction code, whereas the one substantiation would need packet retransmission associate degreed thence an multiplied transmission latency the excellence between permanent and transient errors is granted because of an area historic, that saves the transmission results, and a loopback output mechanism (see Section IV). moreover, our resolution combined with the loopback mechanism and therefore the novel native historic permits the localization of errors, either on the bus connections or within the switches, by localizing the faulty port.

#### ROUTING ERROR DETECTION

The reliable switch being projected incorporates a web routing fault detection mechanism. This approach will operate with adaptive formulas supported the distance vector routing algorithm [3], [12], [14], [20]. The most problem in routing error detection is to tell apart a bypass of associate degree unobtainable part within the secret agent from a true routing error illustrates the challenge for

Fig:Loopback module for existing system

such error detection. except for a rise of the info packet latency, the consequence of the non detection of routing errors is that the attainable loss of knowledge packets being sent either to associate degree already detected faulty router or to a vicinity performing arts a dynamic reconfiguration. so as to realize routing error detection, the projected reliable router depends on diagonal state indications, on further routing info within the header flits, and on the routing error detection blocks in every port the fundamental idea of our approach is that the following: every router receiving an information packet checks the correctness of the routing call created by the previous crossed switch. This routing error detection is performed in parallel when the playacting error correction code, as shown in Fig. 2. Consequently, this detection doesn't increase the info packet latency.

# A. components needed for Routing Error Detection

1) Diagonal accessibility Indications: The RKT-switch uses info links to point to its neighbors its accessibility standing.we have a tendency to outline as unobtainable associate degree input port that can't receive information packets. To preserve the very best turnout of the secret agent, our strategy is to disconnect solely the faulty components of the routers. Thereby, if a router input port is for good faulty, it's disabled whereas maintaining the opposite input ports as active, so as to get a partly in operation switch. On the contrary, if all input ports square measure faulty, the router is taken into account as unobtainable. Similarly, we have a tendency to outline as unobtainable secret agent elements that can't receive information packets owing to permanent faults or a partial

dynamic reconfiguration. The RKT-switch indicates its accessibility standing to the eight direct neighboring routers through the diagonal accessibility indication (DAI) links. The network structure supported DAI links is shown in Fig. 4. These DAI links permit the checking of the correctness of the routing formula. Indeed, every router is in a position to regulate the provision standing of the neighboring routers and elements for example, in Fig. 4(a), router (i, j) will check the provision of router(i +1, j -1). The network elements (PEs or IPs) don't seem to be allowed to route data packets and square measure restrained to simplyaccept solely information packets

ensured additionally, the placement of the faulty routing formula blocks within the neighboring routers will be deduced from these journals. A permanent error is taken into account once 3 sequential routing errors square measure detected for a selected routing logic block.

2) Structure of knowledge Fields within the information Packets: A slippery gather data (SGD) field is supplementary to every header flit of the info packets being transmitted. Table I details the structure of an information packet. A flit-type bit is employed to tell apart the header from the info flits. The SGD field contains the addresses of the previous and penultimate crossed routers every router receiving an information packet checks this SGD field and validates the routing alternative created by the previous router to realize the routing validation, the SGD field is updated by every router crossed on the transmission path.

## B. Principle of the Routing Error Detection

Distance vector routing rule is employed once the desired parts square measure on the market within the case of associate degree untouchable part, a selected routing path is regionally chosen to bypass its position once a router receives a knowledge packet, it checks the correctness created by the routing call of the previous node, mistreatment the routing error detection rule. From address comparisons, the router checks if the previous routing call obeyed the gap vector routing rule. Flit is that the case, then the previous call is

meant for them; thence, their DAI interconnections square measure set.

3) Journal of Routing Error Localizations: every routing error detection block of the router inputs owns 3 journals to stay the routing error detection results. These journals square measure associated with the routing logic blocks of the neighboring router connected to the thought-about input port. The West routing error detection block of router(i, j) has 3 journals love the West, North, and South routing blocks of the router(i-1, j) because of these journals, the excellence between permanent and transient errors will be

correct. Otherwise, the router decides whether or not the previous call may be a bypass call or a routing error. The detection rule is needed to see the supply of the router through that the information packets ought to have passed per the sex chromosome rule. This verification is performed because of the DAI links. If the router within the sex chromosome path is untouchable, the previous router call was an accurate bypass. If it's on the market, the previous router call may be a routing error within the latter case, the router adds one "1" to the error journal related to the faulty routing logic block. The position of the faulty block is deduced from the address of the penultimate router within the SGD field. If 3 consecutive errors square measure performed by identical faulty routing logic block, a permanent error is taken into account. During this scenario, a selected knowledge packet is generated towards the switch generating the routing errors. This specific one-flit knowledge packet indicates the faulty input port of the thought of router that has got to be disconnected. For NoCs supported multi flit knowledge packets, it's going to happen that a flit is received while not being preceded by a header flit, that is associate degree incorrect scenario. within the planned RKT-NoC, there's a trifle in every flit indicating whether or not the flit may be a header flit or a knowledge flit, as represented in Table I. once a router receives the primary flit of a knowledge packet, it checks once the playing cryptography, if not the flit is destroyed. Therefore once receiving a knowledge packet, the destination information science or alphabetic character counts the amount of received flits.

Fig:Proposed loopback module

## LOOPBACK MODULE

# A. Basic Principles

In a dynamic reconfigurable NOC, the position and also the range of parts within the network will amendment throughout operation, as illustrated in Fig. 1. Actually, the amount and position of the alphabetic character and information science within the NOC are often dynamically changed so as to satisfy the wants of the appliance. Partial reconfigurable regions (PRRs) should be outlined within the FPGA so as to attain dynamic reconfiguration of the 2-D mesh NOC [24]. These PRRs square measure the regions wherever partial reconfigurable modules (PRMs) are often enforced. PRMs represent electronic instantiations of practical units they're outlined by specific partial bit streams and may be placed per the appliance wants [24]. In observe, these PRMs correspond to the PEs and IPs being enforced and placed within the dynamic NOC, as illustrated in Fig. 1. in an exceedingly reliable NOC, faulty routers square measure isolated at runtime throughout the network operations allow us to take into account a permanent faulty router that can't be corrected. This router is for good disabled. Similarly, throughout the reconfiguration of a PRR, no packet are often sent within the world being reconfigured. Thus, these PRRs square measure dynamically isolated. However, these isolations will result in knowledge packet losses or increase packet transmission latency. a lot of exactly, these drawbacks occur once routers containing knowledge packets in their output buffers have their neighboring nodes untouchable attributable to a dynamic reconfiguration or permanent fault detection. Thereby, these knowledge packets stay keep within the output routers till the top of the reconfiguration (dynamic implementation case) or square measure lost, within the case of detection of a permanent faulty node. to beat these drawbacks, the planned

RKT-switch contains output buffer blocks related to loopback modules, as delineated in Fig. 2. The role of every loopback module is to empty the buffers of every output port by process back the information packets within the input port of the router (more details within the Section IV-C). The result's that the coiled back packets square measure rerouted towards another output port of the router. This avoids knowledge packets changing into treed once a neighboring switch is detected as for good faulty, and reduces latency once a neighbor has suffered a dynamic reconfiguration. Fig. five illustrates the role of a loopback module. A alphabetic character or information science electrode sends knowledge packets towards a destination information science per the sex chromosome routing rule. If suddenly router (1, 3) becomes untouchable, the information packets remaining within the West output of router (2, 3) square measure coiled back and rerouted towards its South output. This mechanism permits the keep knowledge packets to be routed to the destination. Therefore, with router(1, 3) being marked as untouchable, the following knowledge packets coming back from the East input port square measure routed directly towards the South port by the dynamic routing rule. what is more, the most advantage of the combined use of the planned loopback module, the native historic of information errors, and also the switch-to-switch knowledge error detection mechanism is that the precise localization and distinction of the sources of information.

#### B. Design of the Loopback Module

A loopback module is enforced in every of the four ports of the router, as illustrated in Fig. 2. The design of the loopback module is portrayed in Fig. 6. The logic management block checks the provision of the neighboring router so as to transmit the info packets (data request in signal). If no loopback is needed, a semi-crossbar connects the buffer to the

info out signal so as to send the info packets towards the neighboring router and activates the info request out signal. Next, a multiplexor connects the computer file bus to the info in bus. Once a loopback is needed, thanks to the inconvenience of a neighboring router or associate output block request incidence when 3 Nack receptions, the logic management block configures the semi-crossbar block to send the thought-about information packet on the info loopback bus. Therefore, the info packet is whorled back within the router and can be thought-about as a brand new packet throughout this step, so as to avoid the reception of a brand new information packet from the neighboring switch, the out signal is activated. The loopback module needs one clock cycle to be crossed. Thereby, an information packet crossing a router has its latency exaggerated by 2 clock cycles. Indeed, 2 loopback modules area unit crossed: one once inward and one once exploit the switch.

#### CONCLUSION

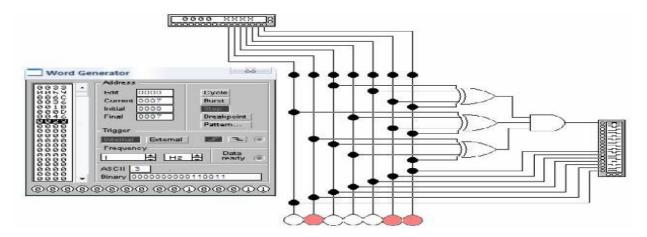

In this paper, we tend to planned new error detection mechanisms for dynamic NoCs. The planned routing error detection mechanisms permit the correct localization of permanent faulty routing blocks within the network. they're appropriate for routing algorithms supported distance vector algorithm wherever the most problem is to tell apart the bypasses of Associate in Nursing unobtainable element within the intelligence officer from real routing errors .Validation simulations of our planned routing error detection showed a routing error localization near ninety six for routing errors on Associate in algorithmic program supported distance vector routing algorithm relating to the planned knowledge packet error localization mechanisms, the simulations conferred during this paper clearly show the potency of our techniques, which may localize permanent sources of errors additional accurately than the switch-to switch or code-disjoint mechanisms. Moreover, each conferred techniques will distinguish permanent and transient errors, and show enticing performance as conferred within the FPGA synthesis comparisons with a non reliable .Our in progress work focuses on evaluating accurately the impact of faulty detection blocks and rising the routing error detection mechanisms, by protective the DAI links and routing detection blocks against errors.

## **REFERENCES**

[1] K. Sekar, K. Lahiri, A. Raghunathan, and S. Dey, "Dynamically configurable bus topologies for high-performance on-chip communication," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 16, no. 10,pp. 1413–1426, Oct. 2008.

- [2] J. Shen and P. Hsiung, *Dynamic Reconfigurable Network-on-ChipDesign: Innovations for Computational Processing and Communication*, J. Shen and P. Hsiung, Eds. Hershey, PA, USA: IGI Global, 2010.

- [3] G.-M. Chiu, "The odd-even turn model for adaptive routing," *IEEETrans. Parallel Distrib. Syst.*, vol. 11, no. 7, pp. 729–738, Jul. 2000.

- [4] Y. M. Boura and C. R. Das, "Efficient fully adaptive wormhole routing inn-dimensional meshes," in *Proc. 14th Int. Conf. Distrib. Comput. Syst.*, Jun. 1994, pp. 589–596.

- [5] C. Bobda, A. Ahmadinia, M. Majer, J. Teich, S. Fekete, and J. van derVeen, "DyNoC: A dynamic infrastructure for communication in dynamically reconfigurable devices," in *Proc. Int. Conf. Field Program. LogicAppl.*, Aug. 2005, pp. 153–158.

- [6] T. Pionteck, R. Koch, and C. Albrecht, "Applying partial reconfiguration to networks-on-chip," in *Proc. Field Program. Logic Appl. Int. Conf.*, Aug. 2006, pp. 1–6.

- [7] S. Jovanovic, C. Tanougast, and S. Weber, "A new high-performance scalable dynamic interconnection for fpga-based reconfigurable systems."

- in *Proc. Int. Conf. Appl.-Specific Syst.*, *Archit. Process.*,Jul. 2008,pp. 61–66.

- [8] S. Jovanovic, C. Tanougast, C. Bobda, and S. Weber, "CuNoC: A dynamic scalable communication structure for dynamically reconfigurable FPGAs," *Microprocess. Microsyst.*, vol. 33, no. 1, pp. 24–36,Feb. 2009.

- [9] P. Lysaght and J. Dunlop, "Dynamic reconfiguration of FPGAs," in *Proc. Int. Workshop Field Program. Logic Appl. More FPGAs.* 1994,pp. 82–94.

- [10] J. Wu, "A fault-tolerant and deadlock-free routing protocol in 2d meshes based on odd-even turn model," *IEEE Trans. Comput.*, vol. 52, no. 9, pp. 1154–1169, Sep. 2003.

- [11] D. Park, C. Nicopoulos, J. Kim, N. Vijaykrishnan, and C. Das, "Exploring fault-tolerant network-on-chip architectures," in *Proc. Int. Conf.Depend. Syst. Netw.*, Jun. 2006, pp. 93–104. [12] S. Jovanovic, C. Tanougast, S. Weber, and C. Bobda, "A

- new deadlock-free fault-tolerant routing algorithm for NoC interconnections," in *Proc. Int. Conf. Field Program. Logic Appl.*, Aug.—Sep. 2009, pp. 326–331.

- [13] D. Fick, A. DeOrio, G. Chen, V. Bertacco, D. Sylvester, and D. Blaauw,

- "A highly resilient routing algorithm for fault-tolerant NoCs," in *Proc. Design, Autom. Test. Eur. Conf. Exhibit.*, Apr. 2009, pp. 21–26.

- [14] W. Dally and C. Seitz, "Deadlock-free message routing in multiprocessor interconnection networks," *IEEE Trans. Comput.*, vol. C-36, no. 5, pp. 547–553, May 1987.

- [15] M. Hosseinabady, M. Kakoee, J. Mathew, and D. Pradhan, "Low latency and energy efficient scalable architecture for massive NoCs using generalized de Bruijn

- graph," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 8, pp. 1469–1480, Aug. 2011.

- [16] C. Grecu, L. Anghel, P. Pande, A. Ivanov, and R.Saleh, "Essential faulttolerance metrics for NoC infrastructures," in *Proc. Int. On-Line Test. Symp.*, 2007, pp. 37–42.

- [17] A. P. Frantz, L. Carro, E. Cota, and F. L. Kastensmidt, "Evaluating SEU and crosstalk effects in network-on-chip routers," in *Proc. 12th IEEE Int. Symp. On-Line Test.*, Jul. 2006, pp. 191–192. interconnects," in *Proc. 12th IEEE Int. On-Line Test. Symp.*, Jul. 2006, pp. 145–150.

- [19] N. Karimi, A. Alaghi, M. Sedghi, and Z. Navabi, "Online networkon- chip switch fault detection and diagnosis using functional switch faults," *J. Universal Comput. Sci.*, vol. 14, no. 22, pp. 3716–3736,2008.

- [20] M. Majer, C. Bobda, A. Ahmadinia, and J. Teich, "Packet routing in dynamically changing networks on chip," in *Proc.* 19th IEEE Int. Parallel Distrib. Process. Symp., Apr. 2005, p. 154b.