# AN EFFICIENT 3D DETAILED ROUTER APPLYING REGULAR ROUTING PATTERNS

S.R.Subathra<sup>1,</sup> S.B.Subbulakshmi<sup>2,</sup> R.Sujitha<sup>3,</sup> B.Tech Scholar, ECE Department, Kalasalingam University subathrasr6@gmail.com, subbulakshmisb94@gmail.com, lithikasujisri@gmail.com

K.Pandiaraj<sup>4</sup> M.E, Assistant Professor II, ECE Department, Kalasalingam University pandiaraj@klu.ac.in Dr. P. Sivakumar<sup>5</sup>

Assistant Professor,

ECE Department,

Kalasalingam University

siva@klu.ac.in

#### ABSTRACT:

VLSI generally consists of partitioning, placing and routing. Routing is interconnecting local nets with a set of wires. It could be done only in dead space or white space and cannot be routed if there is a blockage. It is of two types namely Global Routing and Detailed Routing. With Global Routing as base Detailed Routing is to be done. Detailed router is made to follow regular routing patterns and a regular route is applied for better design and rule satisfactory in order to avoid jogs and detours. Here 2D Detailed routing tracks, spacing based design rules are to be discussed. Routing of local nets are to be done before global segment assignment using bottom up layer by layer and panel by panel framework. To reduce congestion Panel Merging and Maze Routing techniques are to be used. With the help of benchmark circuits label position and congestion prevailing among local nets are to be determined. Reducing the white or dead space is to be done by Panel Merging technique.

# INTRODUCTION:

A router needs to be an efficient one. Efficiency deals with time, delay, speed and power. If these are efficient a system is said to be efficient. But this is not practically possible as it consists of a lot of constraints as jogs, detours and blockages. In order to make an efficient router VSRT, bottom up layer by layer, Panel Merging and MWIS techniques are to be used. While routing from a source to a destination it could be routed only through white space or dead space not through obstacles. To make a route as an efficient one shortest path has to be chosen along with a regular routing pattern making the routing process easier. Regular Routing also introduces less wire length improvising time, signal integrity and power consumption. Routing of each net could be done using maze routing along with rip-up and re-route technique. Regular route performances are to be analyzed from ISPD98 benchmarks.

# PROBLEM FORMULATION:

Inputs are based on underlying spacing based rules, 2D global routing solution. If a 2D global routing solution is

to perform automatically layer assignment and detailed routing is solved. The main objective is to connect and route as many nets as possible. In general global routing generates 3D solution where it is more restrictive with a lot of constraints. It does not provide relevant information to perform layer assignment and local nets are also not captured. Where detailed routing captures both local nets and global segments. It should be noted that each segment has to be assigned to a track to make it less restrictive, assignment to more than one track also occurs but it is not preferable.

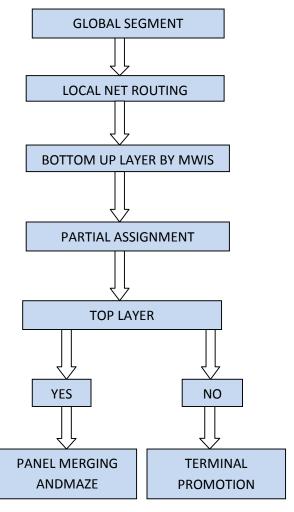

#### **ALGORITHM FLOW:**

The process starts with extracting all global segments. And routing of local nets has to be done before global segment assignment or else it leads to blockages. A number of layers constitutes to a single panel. And routing has to be done from bottom layer, the last layers of the upper panel and the upper layers of the bottom panel remains unrouted. Maze routing techniques can be implied for those unrouted portion supported with rip-up and re-route technique. It is very effective in finding the label position of local net with the help of benchmark circuit and it is used to reduce the white space prevailing. If panels are merged, then routing becomes easier and regular routing patterns could be used without any constraints.

Then each layer is assigned with a certain weight and based on the priority routing is done. If it is an unrouted top layer Panel Merging and Maze Routing is done.

# ALTERNATIVE FLOWS AND DISCUSSION:

Local nets could be routed by using vertical spine routing topology also. This helps to find out the interconnection properties to route mainly the local nets. It has its structure with x co-ordinate which is the median of all pins where each pin is connected to a central spine and based on weight of each pins routing is performed and leads to complexity of time. It routes as many nets as possible also constitutes in wire length minimization.

Always local nets has to be assigned before global segment assignment. This could be done by MWIS and solved by fast and effective heuristic optimization methods.

# ROUTING CONSIDERATIONS: NUMBER OF TERMINALS:

Majority of nets are two terminal ones and for some nets like clock and power, number of terminals can be large. Always each multi terminal net can be decomposed into several two terminal nets.

#### **NET WIDTH:**

Power and ground nets has greater width and signal nets has less width.

Fig 1. ALGORITHM FLOW

# **VIA RESTRICTIONS:**

It is of two types namely regular which could be done only between two layers and stacked which could be done through more than two layers.

#### **BOUNDARY TYPE:**

It is of two types namely regular and irregular. It is also based on the net types and the number of layers.

# **UNASSIGNED SEGMENTS:**

The probability of unassigned segments mainly occurs at top layers. And to improve the routability Panel Merging and Maze Routing is applied. Congestion is also prevented being more flexible. In Panel Merging technique one panel is merged with the neighboring panel and can be adjusted based on hardness level and runtime. It is more effective for the segment nearer to the panel boundary. At first, routing has to be done from lower layers and for unrouted portions line probing maze routing technique could be applied.

#### **RESULTS AND DISCUSSIONS:**

Experiments were performed based on the ISPD98benchmark results.

#### **RESULTS OF REGULAR ROUTE FOR ISPD98:**

This benchmark circuit consists of .net, .are, .netD file format. Each format consists of 22,500 modules, nets and pins. We worked to split those modules and read those using C and Matlab to convert those modules into array format to find the pin connections. All those connections were made as a grid graph pointing o of a label. And layers could be analyzed along with label position. But those local nets position in terms

We worked to merge all those layers reducing the white space to make routability effective. Congestion also could be controlled if a proper layer assignment is done.

# **OUTPUT:**

### CONCLUSION:

We have performed on the unassigned portions finding the local nets positions on a grid graph with ISPD98 results. Thereby decreasing the white space, congestion, local nets,

and wire length also. Our upcoming works will be to find the critical path, time, phase, delay and to merge out panels.

# ACKNOWLEDGEMENT:

We thank the Department of Electronics and Communication Engineering of Kalasalingam University, (Kalasalingam Academy of Research and Education), Tamil Nadu, India for permitting to use the computational facilities available in Centre for Research in Signal Processing and VLSI Design which was setup with the support of the Department of Science and Technology (DST), New Delhi under FIST Program in 2013.

#### **REFERENCES:**

- 1. M. Gester, D. Muller, T. Nieberg, C. Panten, C. Schulte, and J. Vygen, "Algorithms and data structures for fast and good VLSI routing," in Proc. ACM/IEEE Design Autom. Conf., Jun. 2012, pp. 459–464.

- 2. Y. Zhang and C. Chu, "GDRouter: Interleaved global routing and detailed routing for ultimate routability," in *Proc. ACM/IEEE Design Autom. Conf.*, Mar. 2012, pp. 597–602.

- 3. J. Gao and D. Pan, "Flexible self-aligned double patterning aware detailed routing with prescribed layout planning," in *Proc. ACM/SIGDA Int. Symp. Phys. Design*, 2012, pp. 25–32.

- 4. Y. Lin, Y. Ban, D. Pan, and Y. Li, "DOPPLER: DPL-aware and OPC- friendly gridless detailed routing with mask density balancing," in *Proc. Int. Conf. Comput.-Aided Design*, 2011, pp. 283–289.

- D. Ding, J. Gao, K. Yuan, and D. Pan, "AENEID:A generic lithography-friendly detailed router based on post-RET data learning and hotspot detection," in *Proc. ACM/IEEE Design Autom. Conf.*, Jun. 2011, pp.795–800.

- 6. Y. Zhang and C. Chu, "RegularRoute: An efficient detailed router with regular routing patterns," in *Proc. ACM/SIGDA Int. Symp. Phys. Design*,2011, pp. 45–52.

- 7. D. Pan, M. Cho, and K. Yuan, "Manufacturability aware routing in nanometer VLSI," *Found Trends Electron. Design Autom.*, vol. 4, no. 1, pp. 1–97, Jan. 2010.

- 8. M. Ozdal, "Detailed-routing algorithms for dense pin clusters in inte-grated circuits," *IEETrans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 28, no. 3, pp. 340–349, Mar. 2009.

- 9. Y. Zhang and C. Chu, "CROP: Fast and effective congestion refinement of placement," in *Proc. Int. Conf. Comput.-Aided Design*, 2009, pp. 344–350.

- 10. Y. Xu, Y. Zhang, and C. Chu, "FastRoute 4.0: Global router with efficient via minimization," in *Proc. Asia South Pacific Design Autom. Conf.*, 2009, pp. 576–581.