### Design of high speed Dynamic Dual rail double tail latch Comparator

## P.SORNA SARASUWATHY M.E VLSI DESIGN J.P.COLLEGE OF ENGINEERING

Abstract: - Modern communication and signal processing is dependent on the high speed and low power consumption of the Analog-to-Digital converters (ADC) to a very large extent. Comparator is the basic building block of the ADCs which compares the two set of variables and change the input analog signal in digital. In this paper a new design of double tail comparator is proposed for high frequency of data conversion and is compared with the best available recently proposed double tail comparator design in term of area on chip power utilization, delay consideration. The proposed topology is based on two cross coupled differential pairs positive feedback and switchable current sources, has a lower power dissipation, higher speed, less area, and it is shown to be very robust against transistor mismatch, noise immunity. A new CMOS dynamic comparator using dual input single output differential amplifier as latch stage suitable for high speed analog-to-digital converters with High Speed, low power dissipation and immune to noise. This topology completely removes the noise that is present in the input. The structure shows lower power dissipation and higher speed than the conventional comparators.

#### I.INTRODUCTION

Due to fast speed, low power consumption, high input impedance and full-swing output, dynamic latched comparators are very attractive for many applications such as high-speed analog-to digital converters (ADCs), memory sense amplifiers (SAs) and data receivers. They use positive feedback mechanism with one pair of back-to-back cross coupled inverters (latch) in order to convert a small inputvoltage difference to a full-scale digital level in a short time. However, an input-referred latch offset voltage, resulting from static mismatches such as threshold voltage Vth and !Cox variations in the regenerative latch, deteriorates the accuracy of such comparators. Moreover, dynamic mismatch from the unbalanced parasitic capacitances on the output nodes of the latch causes the additional offset term during evaluation phase [5], [6]. Because of this reason, the input referred latch offset voltage is one of the most important design parameters of the latched

comparator. If large devices are used for the latching stage, a low offset can be achieved at the cost of the reduced speed due to slowing the regeneration time and the increased power dissipation. More practically, the input-referred latch offset voltage can be reduced by using the pre-amplifier preceding the regenerative output latch stage as shown in

# MR.P.JOHN BOSCO AP/ECE DEPARTMENT J.P.COLLEGE OF ENGINEERING

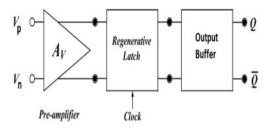

Figure 1. It can amplify a small input voltage difference to a large enough voltage to overcome the latch offset voltage. However, the preamplifier based comparators suffer not only from large power consumption for a large bandwidth but also

Figure 1 Typical block diagram of a high-speed voltage comparator

from the reduced intrinsic gain with a reduction of the drain-to-source resistance *rds* due to the continuous technology scaling [7]. In this paper, we present a new dynamic latched comparator which shows lower input-referred latch offset voltage and higher load drivability than the conventional dynamic latched comparators. With two additional inverters inserted between the input- and output-stage of the conventional double-tail dynamic comparator, the gain preceding the regenerative latch stage was improved and the complementary version of the output-latch stage, which has bigger output drive current capability at the same area, was implemented.

The remaining sections of the paper are organized as follows. Section II provides an overview of the previous works about the dynamic comparators in terms of their advantages and drawbacks, and section III describes the proposed dual rail dynamic latched comparator which is based on the structures from [3], [4]. Results from PSPICE with *VDD*=1V presented in Section IV and conclusion is present in Section V.

#### II. DYNAMIC COMPARATORS

Clocked regenerative comparators have found wide applications in many high-speed ADCs since they can make fast decisions due to the strong positive feedback in the regenerative latch. Recently, many comprehensive analyses have been presented, which investigate the performance of

these comparators from different aspects, such as noise [11], offset [12], [13], and [14], random decision errors [15], and kick-back noise [16]. In this section, a comprehensive delay analysis is presented; the delay time of two common structures, i.e., conventional dynamic comparator and conventional dynamic double-tail comparator are analyzed, based on which the proposed comparator will be presented.

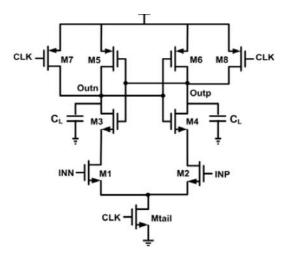

Fig. 2. Schematic diagram of the conventional dynamic comparator.

#### A. Conventional Dynamic Comparator

The schematic diagram of the conventional dynamic comparator widely used in A/D converters, with high input impedance, rail-to-rail output swing, and no static power consumption is shown in Fig. 1 [1], [17]. The operation of the comparator is as follows. During the reset phase when CLK = 0 and Mtail is off, reset transistors (M7–M8) pull both output nodes Outn and Outp to VDD to define a start condition and to have a valid logical level during reset. In the comparison phase, when CLK = VDD, transistors M7 and M8 are off, and Mtail is on. Output voltages (Outp, Outn), which had been pre-charged to VDD, start to discharge with different discharging rates depending on the corresponding input voltage (INN/INP). Assuming the case where VINP > VINN, Outp discharges faster than Outn, hence when Outp (discharged by transistor M2 drain current), falls down to VDD |Vthp| before Outn (discharged by transistor M1 drain current), the corresponding pMOS transistor (M5) will turn on initiating the latch regeneration caused by back-to-back inverters (M3, M5 and M4, M6). Thus, Outn pulls to VDD and Outp discharges to ground. If VINP < VINN, the circuits works vice versa. As shown in Fig. 2, the delay of this comparator is comprised of two time delays, t0 and tlatch. The delay t0 represents the capacitive discharge of the load capacitance CL until the first pchannel transistor (M5/M6) turns on. In case, the voltage at node INP is bigger than INN (i.e., VINP > VINN), the drain current of transistor M2 (I2) causes faster discharge of Outp node compared to the Outn node, which is driven by M1 with smaller current. Consequently, the discharge delay (t0) is given by

Fig.3.Transient simulations of the conventional dynamic comparator for input voltage difference of Vin = 5 mV, Vcm = 0.7 V, and VDD = 0.8 V.

In (1), since  $I2 = Itail/2 + \_Iin = Itail/2 + gm1, 2$  Vin, for small differential input (Vin), I2 can be approximated to be constant and equal to the half of the tail current. The second term, tlatch, is the latching delay of two cross coupled inverters. It is assumed that a voltage swing of Vout = VDD/2 has to be obtained from an initial output voltage difference V0 at the falling output (e.g., Outp). Half of the supply voltage is considered to be the threshold voltage of the comparator following inverter or SR latch [17]. Hence, the latch delay time is given by, [18]

$$t_{\text{latch}} = \frac{C_{\text{L}}}{g_{m,\text{eff}}} \cdot \ln\left(\frac{\Delta V_{\text{out}}}{\Delta V_{0}}\right) = \frac{C_{\text{L}}}{g_{m,\text{eff}}} \cdot \ln\left(\frac{V_{\text{DD}}/2}{\Delta V_{0}}\right)$$

where gm, eff is the effective trans conductance of the back-to back inverters. In fact, this delay depends, in alogarithmic manner, on the initial output voltage difference at the beginning of the regeneration (i.e., at t = t0). Based on (1),  $\_V0$  can be calculated from (3)

The current difference, Iin = |I1 - I2|, between the branches is much smaller than I1 and I2. Thus, I1 can be approximated by Itail/2 and (3) can be rewritten as

$$V0 = |V \text{thp}| \frac{I \text{in}}{I1}$$

(3)

In principle, this structure has the advantages of high input impedance, rail-to-rail output swing, no static power consumption, and good robustness against noise and mismatch [1]. Due to the fact that parasitic capacitances of input transistors do not directly affect the switching speed of the output nodes, it is possible to design large input transistors to minimize the offset. The disadvantage, on the other hand, is the fact that due to several stacked transistors, a sufficiently high supply voltage is needed for a proper delay time. The reason is that, at the beginning of the decision, only transistors M3 and M4 of the latch contribute to the positive feedback until the voltage level of one output node has dropped below a level small enough to turn on transistors M5 or M6 to start complete regeneration. At a low supply voltage, this voltage drop only contributes a small gate-source voltage for transistors M3 and M4, where the gatesource voltage of M5 and M6 is also small; thus, the delay time of the latch becomes large due to lower transconductances.

Another important drawback of this structure is that there is only one current path, via tail transistor Mtail, which defines the current for both the differential amplifier and the latch (the cross-coupled inverters). While one would like a small tail current to keep the differential pair in weak inversion and obtain a long integration interval and a better Gm/I ratio, a large tail current would be desirable to enable fast regeneration in the latch [10]. Besides, as far as Mtail operates mostly in triode region, the tail current depends on input common-mode voltage, which is not favorable for regeneration.

#### B. Conventional Double-Tail Dynamic Comparator

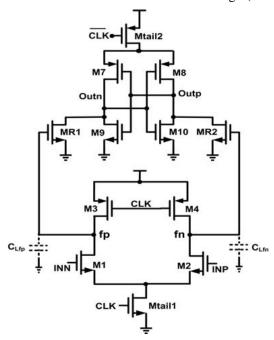

A conventional double-tail comparator is shown in Fig. 3 [10]. This topology has less stacking and therefore can operate at lower supply voltages compared to the conventional dynamic comparator. The double tail enables both a large current in the latching stage and wider *M*tail2, for fast latching independent of the input common-mode voltage (*V*cm), and a small current in the input stage (small *M*tail1), for low offset [10].

The operation of this comparator is as follows (see Fig. 4). During reset phase (CLK = 0, Mtail1, and Mtail2 are off), transistors M3-M4 pre-charge fn and fp nodes to VDD, which in turn causes transistors MR1 and MR2 to discharge the output nodes to ground. During decision-making phase (CLK = VDD, Mtail1 and Mtail2 turn on), M3-M4 turn off and voltages at nodes fn and fp start to drop with the rate defined by IMtail1/Cfn(p) and on top of this, an input-dependent differential voltage Vfn(p) will build up. The intermediate stage formed by MR1 and MR2 passes Vfn(p) to the crosscoupled inverters and also provides a good shielding between input and output, resulting in reduced value of kickback noise [10].

Fig.4. Schematic diagram of the conventional double-tail dynamic comparator.

Similar to the conventional dynamic comparator, the delay of this comparator comprises two main parts, t0 and tlatch. The delay t0 represents the capacitive charging of the load capacitance CLout (at the latch stage output nodes, Outn and Outp) until the first n-channel transistor (M9/M10) turns on, after which the latch regeneration starts; thus t0 is obtained from

$$t0 = \frac{V \text{Thn} C L \text{out}}{I \text{B1}} \quad 2 \frac{V \text{Thn} C L \text{out}}{I \text{tail} 2} \tag{4}$$

where IB1 is the drain current of the M9 (assuming VINP > VINN, see Fig. 3) and is approximately equal to the half of the tail current (Itail2).

After the first n-channel transistor of the latch turns on (for instance, M9), the corresponding output (e.g., Outn) will be discharged to the ground, leading front p-channel transistor (e.g., M8) to turn on, charging another output (Outp) to the supply voltage (VDD). The regeneration time (flatch) is achieved according to (2). For initial output voltage difference at time t0, V0 we have

where gmR1,2 is the trans conductance of the intermediate stage transistors (MR1 and MR2) and Vfn/fp is

the voltage difference at the first stage outputs (fn and fp) at time t0. Thus, it can be concluded that two main parameters which influence the initial output differential voltage ( V0 and thereby the latch regeneration time are the transconductance of the intermediate stage transistors (gmR1,2) and the voltage difference at the first stage outputs (fn and fp) at time t0.

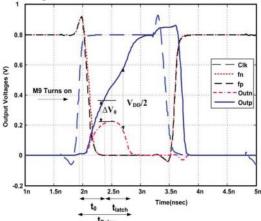

Fig. 5. Transient simulations of the conventional double-tail dynamic comparator for input voltage difference of Vin = 5mV, Vcm = 0.7 V, and VDD = 0.8 V.

The differential voltage at nodes fn/fp ( Vfn/fp) at time t0 can be achieved from

$$Vfn/fp=t0. IN1-IN2 CL,fn(p)$$

(6)

In this equation, IN1 and IN2 refer to the discharging currents of input transistors (M1 and M2), which are dependent on the input differential voltage (i.e., IN = gm1, Vin). Substituting (9) in (8), V0 will be

$$V0 = 2V thn gmR1,2 V0fn/fp$$

(7)

Itail2

This equation shows that V0 depends strongly on the transconductance of input and intermediate stage transistors, input voltage difference (Vin), latch tail current, and the capacitive ratio of CLout to CL, fn(p). Substituting V0 in latch regeneration time (2), the total delay of this comparator is achieved as follows:

tdelay=t0+tlatch

$$= 2 \frac{VThn CLout}{Itail2} + \frac{CLout}{gm,eff} \cdot \ln(VDD/2)$$

(8)

From the equations derived for the delay of the double-tail dynamic comparator, some important notes can be concluded.

1) The voltage difference at the first stage outputs ( Vfn/fp) at time t0 has a profound effect on latch initial differential output voltage ( V0) and consequently on the latch delay.

Therefore, increasing it would profoundly reduce the delay of the comparator.

2) In this comparator, both intermediate stage transistors will be finally cut-off, (since fn and fp nodes both discharge to the ground), hence they do not play any role in improving the effective transconductance of the latch. Besides, during reset phase, these nodes have to be charged from ground to VDD, which means power consumption. The following section describes how the proposed comparator improves the performance of the double-tail comparator from the above points of view.

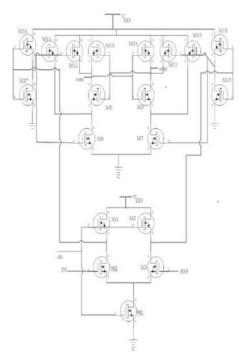

### III.DYNAMIC DUAL RAIL DOUBLE TAIL LATCH COMPARATOR

Circuit Diagram of Proposed Comparator is shown in Figure 5. This circuit mainly is a derived version of the [5]. The back-to-back latch stage is replaced with back-to-back dual input single output differential amplifier. Differential amplifier has so many advantages over the conventional latch which nothing but an inverter. It has higher immunity to

environmental noise and it rejects common mode noise or in other words it has better CMRR. Another property of differential signaling is the increase in maximum achievable voltage swings. It also provides simpler biasing and higher linearity. Main purpose is to eliminating the noise that is present in the latch stage and for which output is getting fluctuated with clock transition.

#### OPERATION OF THE PROPOSED COMPARATOR

During reset phase (clk= 0V), PMOS transistor M4 and M5 turn on and they charge node voltages to VDD. And Hence NMOS transistors M17 and M19 turns on and discharges nodes voltages to GND. Then M14, M15 and PMOS transistors of differential amplifier blocks M12 and M13 turns on, NMOS transistors of differential amplifier block M8, M9 and M6, M7 turns off. The out nodes are charges to VDD.

During evaluation phase (clk= VDD), the node capacitances are discharged from VDD to GND in a rate which is proportional to the input voltages. At a certain voltage of Ni nodes, the inverter pairs M16 /M17 and M18/M19 invert the node signal

Fig. 6. Schematic diagram of the conventional dynamic dual rail double tail latch Comparator.

into a regenerated signal. These regenerated signals turn PMOS transistors M14, M12, M13, and M15 off. And eventually M6, M7, turns on. Hence the back-to-back differential pair again regenerates the node signals and because of M6 and M7 being on, the output latch stage converts the small voltage difference transmitted from node into a full scale digital level output.

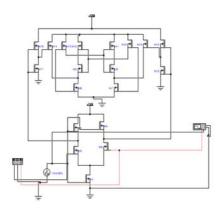

#### IV. RESULT

In order to compare the proposed comparator with the conventional and double-tail dynamic comparators, all circuits have been simulated with VDD = 1V. The comparators were optimized and the transistor dimensions were scaled to get an equal offset standard variation of OS = 8 mV at the input common mode voltage of  $V \, \text{cm} = 1.1 \, \text{V}$  (the same conditions that are found in [10]).

Fig.7. Dynamic dual rail double tail latch Comparator using PSPICE.

#### V.CONCLUSION

A new dynamic comparator using positive feedback shows higher speed, lower power dissipation than the conventional dynamic latched comparators has been proposed & targeted for ADC application. The results are simulated in PSPICE with 90nm CMOS technology. In the proposed design, the back-to-back inverter is replaced with dual input single output differential amplifier in the latched stage. Output of the latch stage in the proposed design is not affected by noise. The noise present in the input and the clock is completely suppressed by the differential amplifiers present in the output latch stage. The proposed structure shows significantly lower power dissipation, higher speed compared to the dynamic comparators present in the literature. The transistor count in the proposed comparator is higher to an extent among all the comparators analyzed.

#### REFERENCES

[1] T. Kobayashi, K. Nogami, T. Shirotori and Y. Fujimoto, "A current-controlled latch sense amplifier and a static power-saving input buffer for low-power architecture," IEEE J. Solid-State Circuits, vol. 28, pp. 523-52, April 1993.

[2] B. Wicht, T. Nirschl, and D. Schmitt Landsiedel, "Yield and speed optimization of

a latch-type voltage sense amplifier", IEEE J. Solid-State Circuits, vol. 39, pp. 1148-1158, July 2004.

[3] D. Schinkel, E. Mensink, E. Kiumperink, E. van Tuijl and B. Nauta, "A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time," ISSCC Dig. Tech. Papers, pp. 314-315 and 605, Feb. 2007.

[4] M. Miyahara, Y. Asada, P. Daehwa and A. Matsuzawa, "A Low-Noise Self- Calibrating Dynamic Comparator for

- High-Speed ADCs," in Proc. A-SSCC, pp. 269-272, Nov. 2008.

- [5] H.J. Jeon, Y.B. Kim, "A Low-offset High-speed Doubletail Dual-rail Dynamic Latched Comparator," ACM GLSVLSI'10(Great Lakes Symposium on VLSI), May 16-18, 2010

- [6] Philip E. Allen and Douglas R. Holberg, CMOS Analog Circuit Design, 2nd ed., Oxford Indian Edition, 2006.

- [7] Jun He, Sanyi Zhan, Degang Chen, and R.L. Geiger, "Analyses of Static and Dynamic Random Offset Voltages in Dynamic Comparators," IEEE Trans. Circuits Syst. I: Reg. Papers, vol. 56, pp. 911-919, May 2009.

- [8] Nikoozadeh and B. Murmann, "An Analysis of Latch Comparator Offset Due to Load Capacitor Mismatch," IEEE Trans. Circuits Syst. II: Exp. Briefs, vol. 53, no.12, pp. 1398-1402, Dec. 2006

- [9] Pedro M.Figueiredo, Joao C.Vital, "Kickback Noise Reduction Techniques for CMOS Latched Comparator", IEEE Transactions on Circuits and Systems, vol.53,no.7, pp.541-545, July 2006.

- [10] B. Murmann et al., "Impact of scaling on analog performance and associated modeling needs," IEEE Trans. Electron Devices, vol. 53, no. 9, pp. 2160-2167, Sep. 2006.

- [11] R. Jacob Baker, Harry W. Li, David E. Boyce, "CMOS- Circuit Design, Layout, And Simulation", IEEE Press Series on Microelectronic Systems, IEEE Press, Prentice Hall of India Private Limited, Eastern Economy Edition, 2002

- [13] Y. Jung, S. Lee, J. Chae, and G. C. Temes, "Low-power and low-offset comparator using latch load," *Electronics Letters*, vol. 47, no. 3, pp.

- 167-168, Feb. 2011.

- [14] M. Miyahara and A. Matsuzawa, "A low-offset latched comparator using zero-static power dynamic offset cancellation technique," in *Proc. IEEE Asian Solid State Circuit Conference*, Taipei, Taiwan, Nov.16-18, 2009, pp. 233–236.

- [15] M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A low-noise self calibrating dynamic comparator for high-speed ADCs," in *Proc. IEEE Asian Solid State Circuit Conference (A-SSCC)*, Fukuoka, Japan, Nov.3-5, 2008, pp. 269–272.

- [16] R. S. Gamad and S. Kale, "Design of a CMOS Comparator for Low

- Power and High Speed," *International Journal of Electronic Engineering Research*, vol. 2, no.1, pp. 29-34, 2010.

- [17] R. S. Gamad, P. Meena, "Low Power and High Speed CMOS Comparator Design Using 0.18µm Technology", *International Journal of Electronic Engineering Research*, vol. 2, no. 1, pp. 71-77, 2010.